# **Chapitre 8**

# **Amplificateurs FET**

# **(transistor á effet de champ)**

Avec permission de Prentice Hall

# Introduction

**Les FETs comportent:**

- **Un excellent gain en tension**

- **Une très haute impédance d'entrée**

- **Petite puissance de consommation**

- **Plage de fréquences assez bonne**

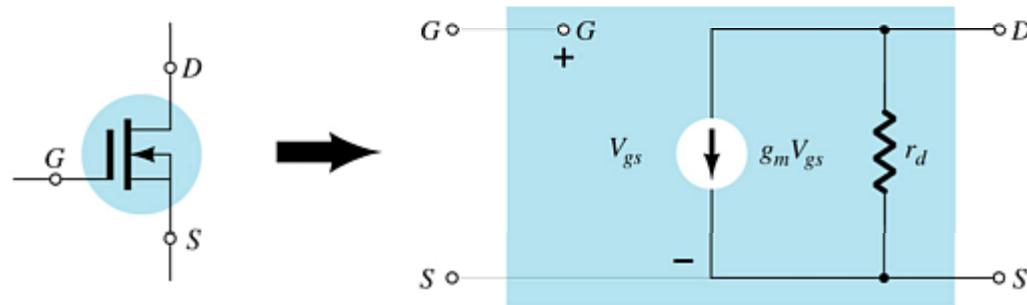

# Modèle petits-signaux des FETs

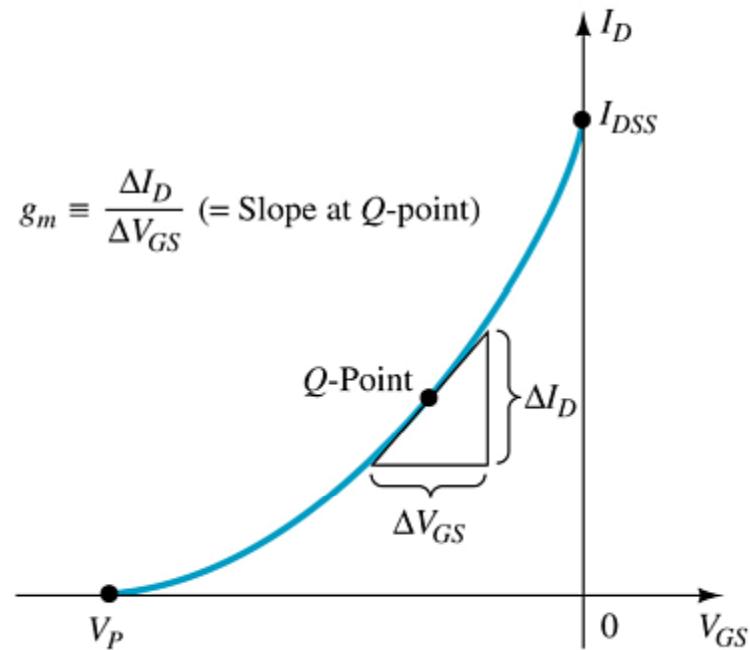

## Transconductance

Le rapport entre un changement de  $I_D$  et un changement correspondant de  $V_{GS}$  s'appelle **transconductance**

La transconductance est représentée par  $g_m$  et elle est donnée par:

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}}$$

# Détermination graphique de $g_m$

# Définitions Mathématiques de $g_m$

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}}$$

$$g_m = \frac{2I_{DSS}}{|V_P|} \left[ 1 - \frac{V_{GS}}{V_P} \right]$$

avec  $V_{GS} = 0V$        $g_{m0} = \frac{2I_{DSS}}{|V_P|}$

$$g_m = g_{m0} \left[ 1 - \frac{V_{GS}}{V_P} \right]$$

avec       $1 - \frac{V_{GS}}{V_P} = \sqrt{\frac{I_D}{I_{DSS}}}$

$$g_m = g_{m0} \left( 1 - \frac{V_{GS}}{V_P} \right) = g_{m0} \sqrt{\frac{I_D}{I_{DSS}}}$$

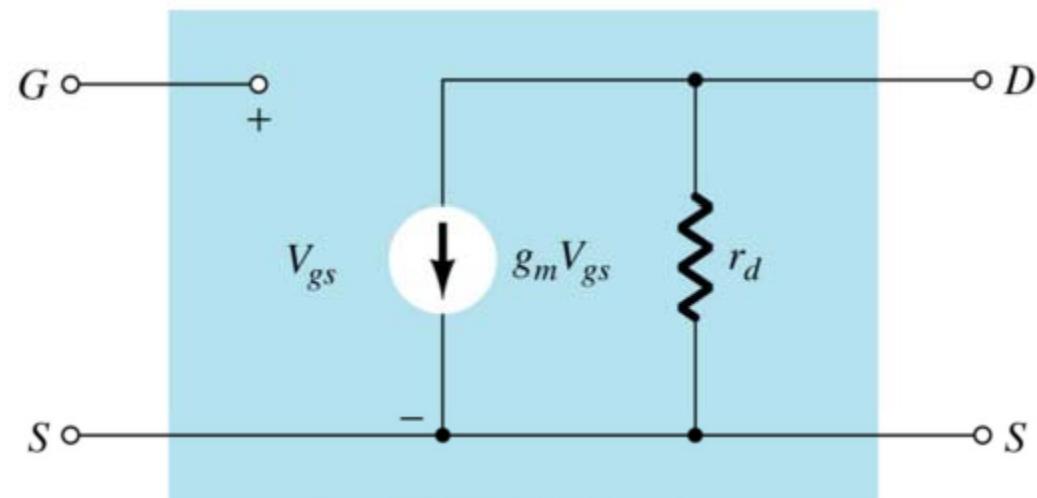

# Impédance FET

**Impédance d'entrée:**

$$Z_i = \infty \Omega$$

**Impédance de sortie:**

$$Z_o = r_d = \frac{1}{y_{os}}$$

**avec:**

$$r_d = \frac{\Delta V_{DS}}{\Delta I_D} \Big| V_{GS} = \text{constant}$$

**$y_{os}$ = admittance selon les specs du FET**

# Circuit Équivalent AC du FET

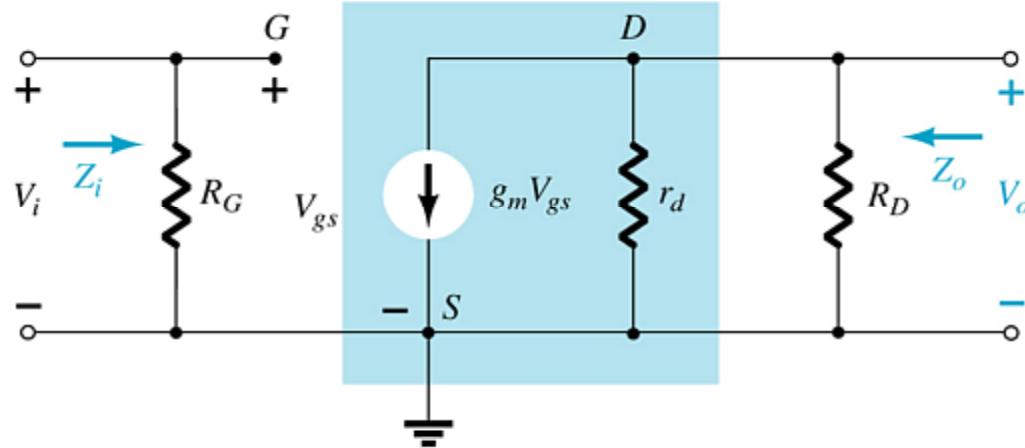

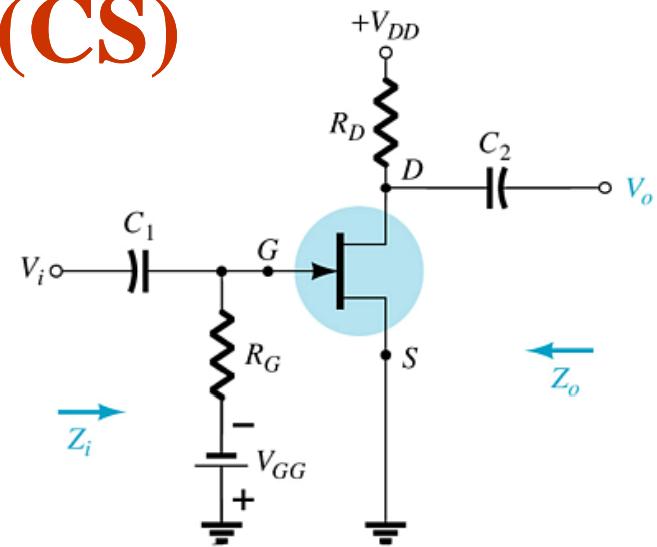

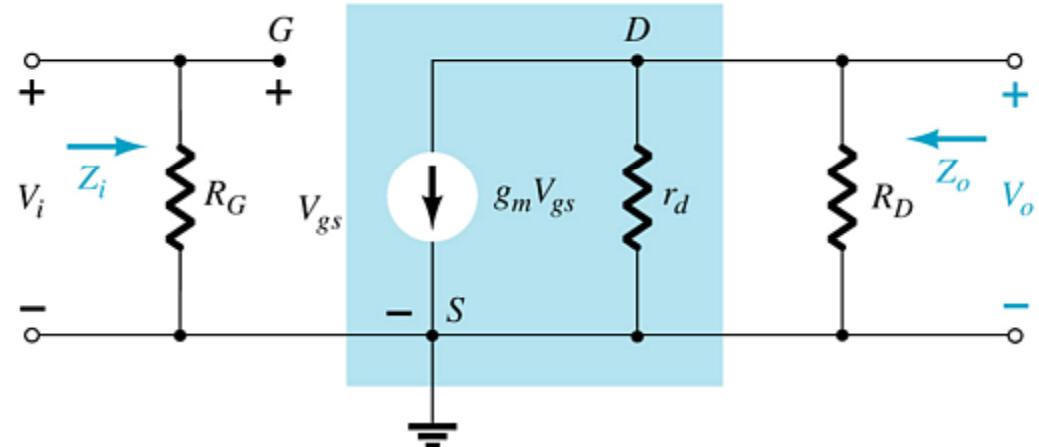

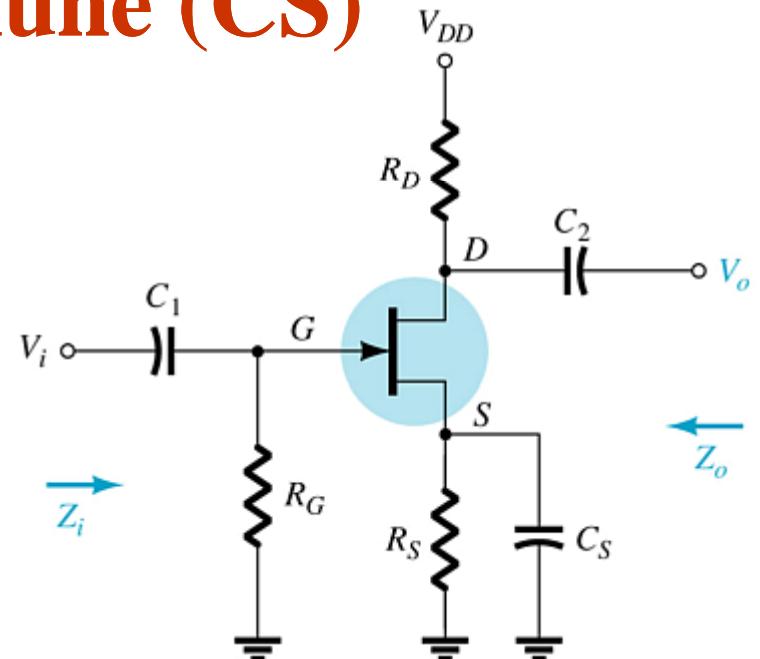

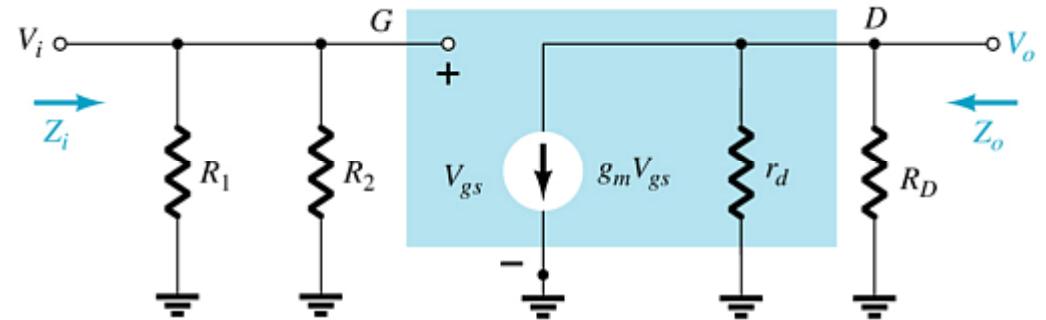

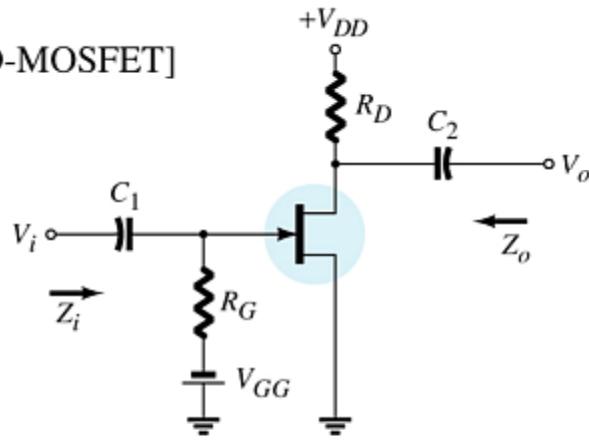

# Circuit par polarisation fixe et Source-Commune (CS)

L'entrée est dans la grille et la sortie est dans le drain

Il y a un changement de phase de  $180^\circ$  entre l'entrée et la sortie.

# Calculs

**Impédance d'entrée:**

$$Z_i = R_G$$

**Impédance de sortie:**

$$Z_o = R_D \parallel r_d$$

$$Z_o \cong R_D \quad \Big| \quad r_d \geq 10R_D$$

**Gain en tension:**

$$A_v = \frac{V_o}{V_i} = -g_m (r_d \parallel R_D)$$

$$A_v = \frac{V_o}{V_i} = -g_m R_D \quad \Big| \quad r_d \geq 10R_D$$

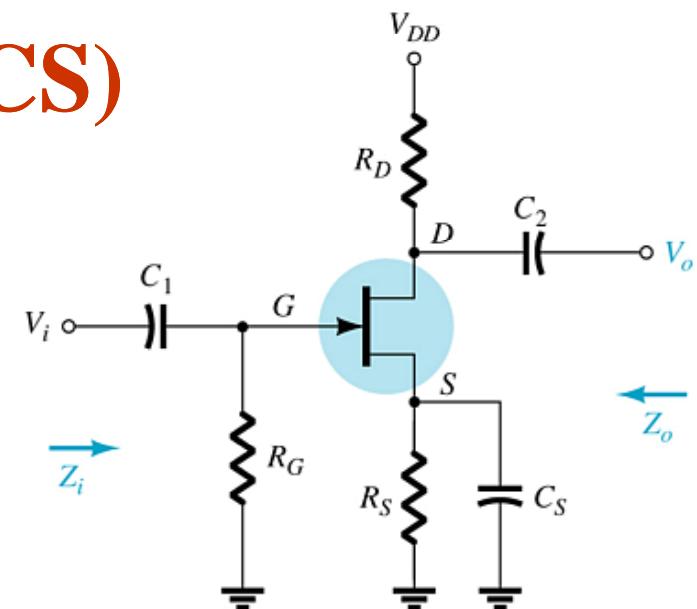

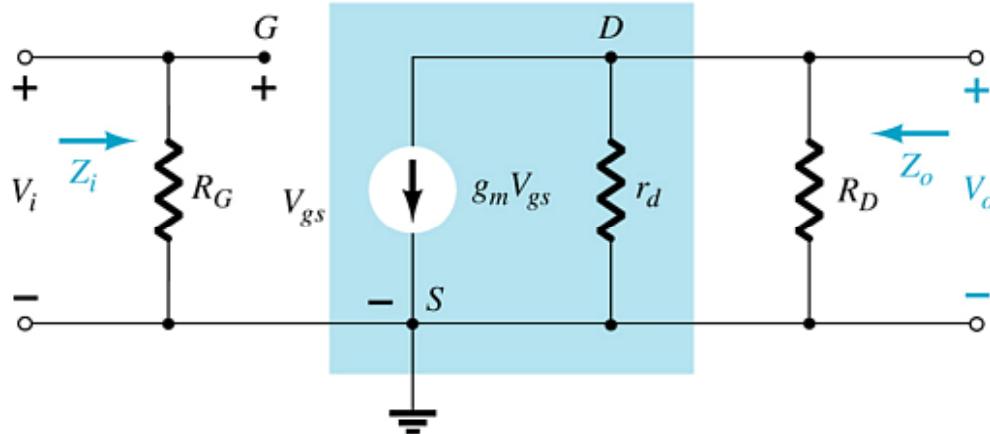

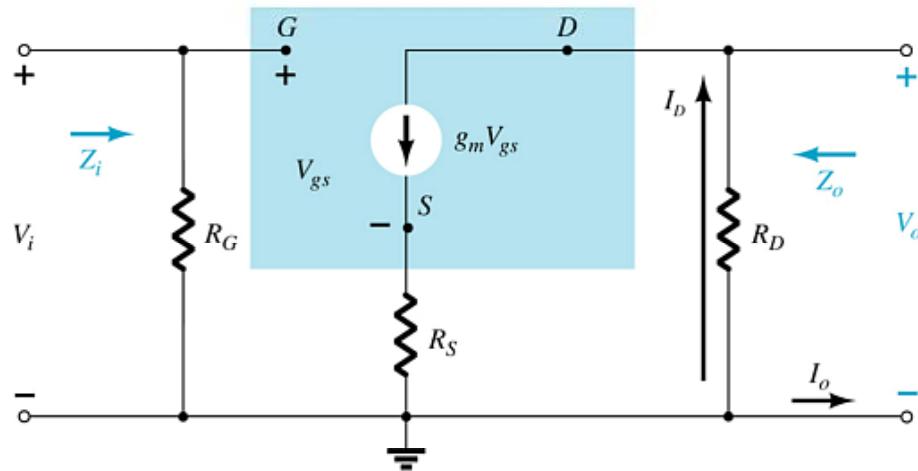

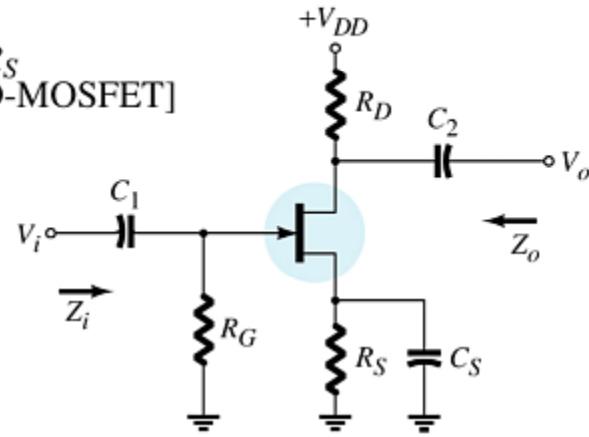

# Circuit par polarisation de masse et Source-Commune (CS)

Voici une configuration à source commune, de façon que l'entrée est dans la grille et la sortie dans le drain.

Il y a un changement de phase de  $180^\circ$  entre l'entrée et la sortie.

# Calculs

Impédance d'entrée:

$$Z_i = R_G$$

Impédance de sortie:

$$Z_o = r_d \parallel R_D$$

$$Z_o \cong R_D \Big|_{r_d \geq 10R_D}$$

Gain en tension:

$$A_v = -g_m (r_d \parallel R_D)$$

$$A_v = -g_m R_D \Big|_{r_d \geq 10R_D}$$

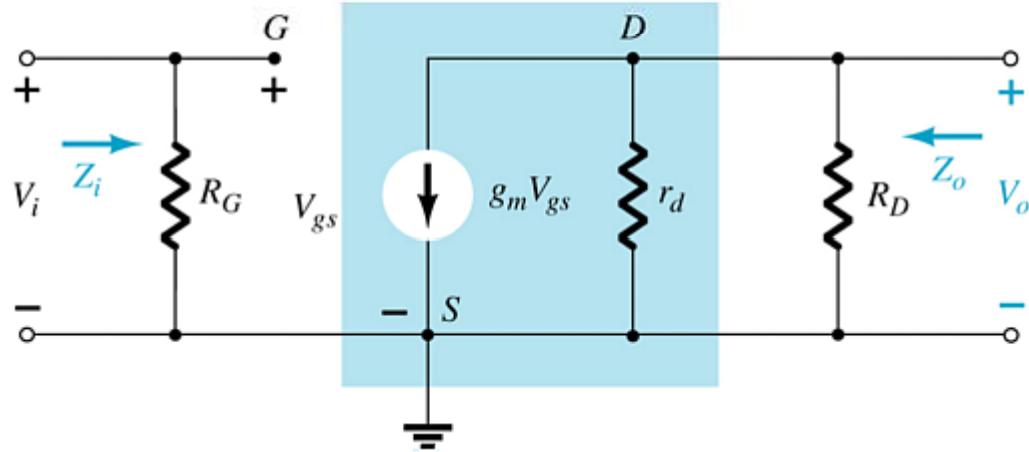

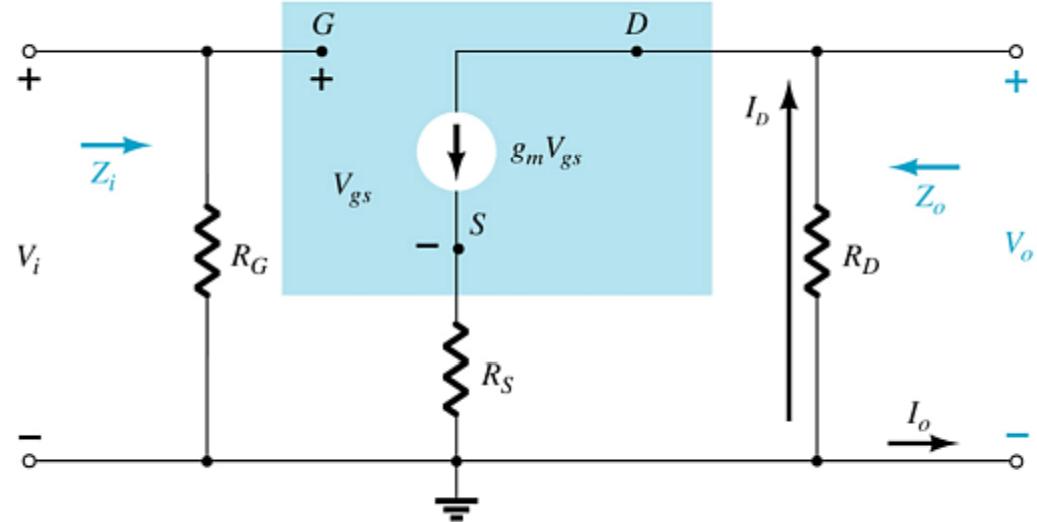

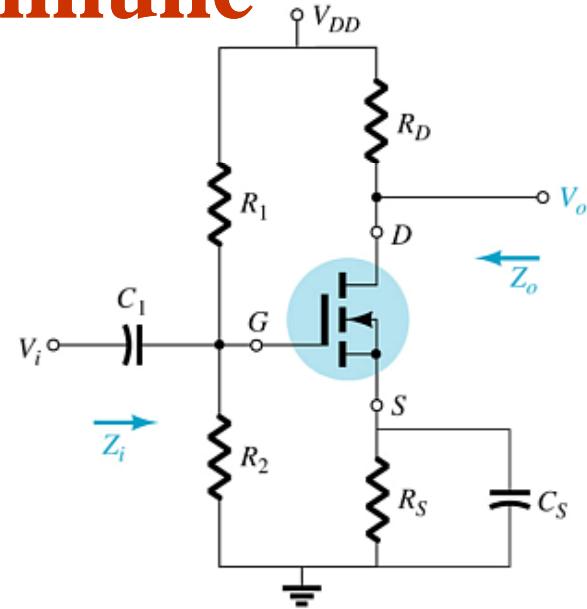

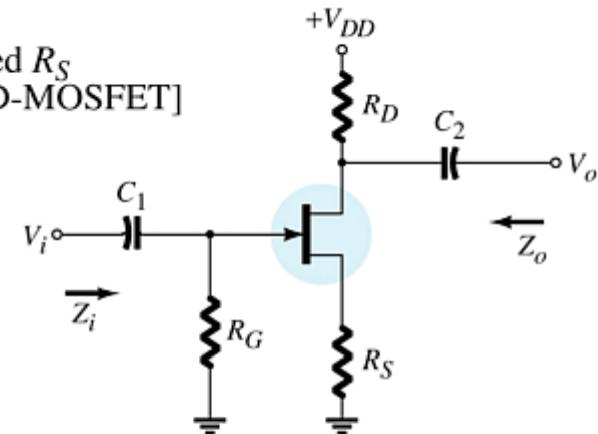

# Circuit de polarisation à la masse, et source-commune (CS)

L'enlèvement de  $C_s$  affecte le gain du circuit.

# Calculs

Impédance d'entrée:

$$Z_i = R_G$$

Impédance de sortie:

$$Z_o \cong R_D \quad \Big| \quad r_d \geq 10R_D$$

Gain en tension:

$$A_v = \frac{V_o}{V_i} = -\frac{g_m R_D}{1 + g_m R_S + \frac{R_D + R_S}{r_d}}$$

$$A_v = \frac{V_o}{V_i} = -\frac{g_m R_D}{1 + g_m R_S} \quad \Big| \quad r_d \geq 10(R_D + R_S)$$

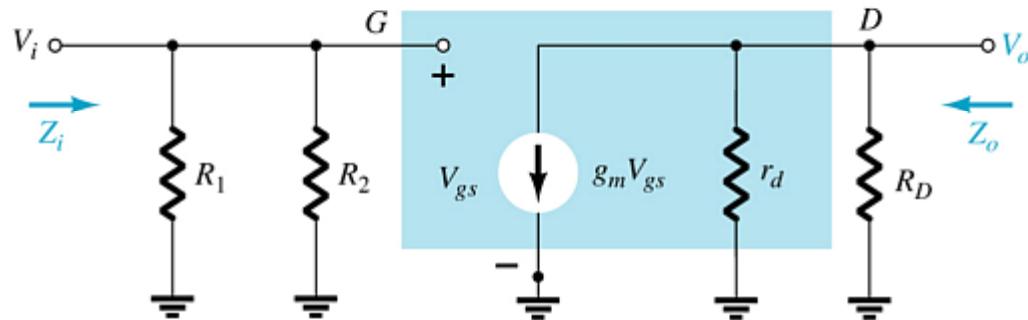

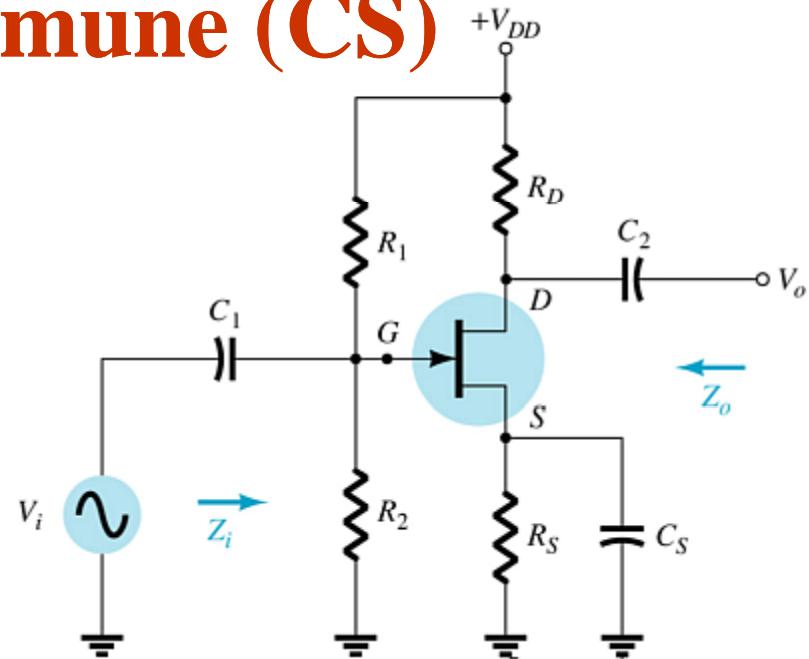

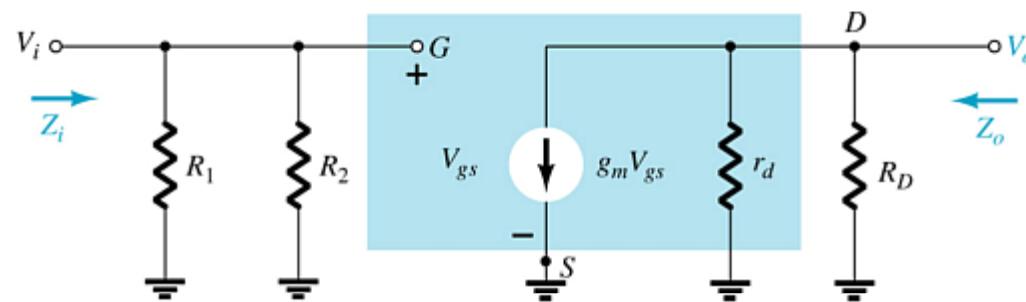

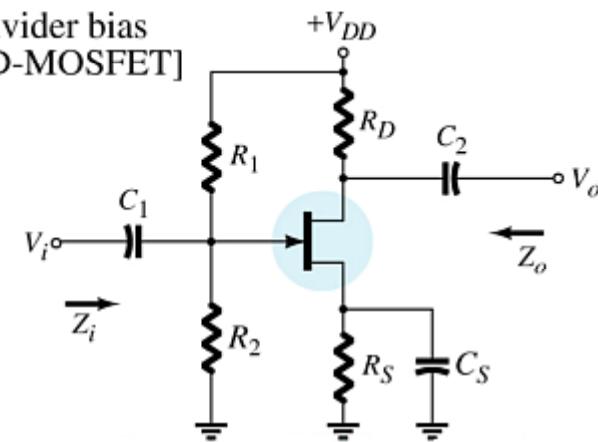

# (CS) Polarisation par diviseur de tension et source-commune (CS)

Voici une configuration à source commune, de façon que l'entrée est dans la grille et la sortie est dans le drain.

# Impédances

Impédance d'entrée:

$$Z_i = R_1 \parallel R_2$$

Impédance de sortie:

$$Z_o = r_d \parallel R_D$$

$$Z_o \cong R_D \Big|_{r_d \geq 10R_D}$$

Gain en tension:

$$A_v = -g_m (r_d \parallel R_D)$$

$$A_v = -g_m R_D \Big|_{r_d \geq 10R_D}$$

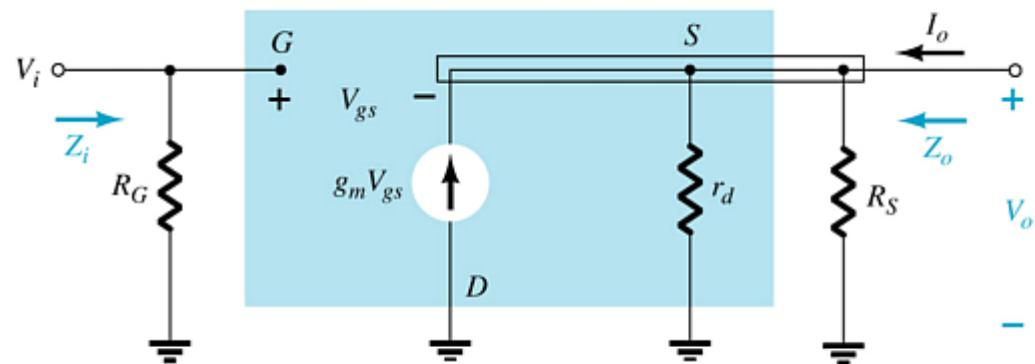

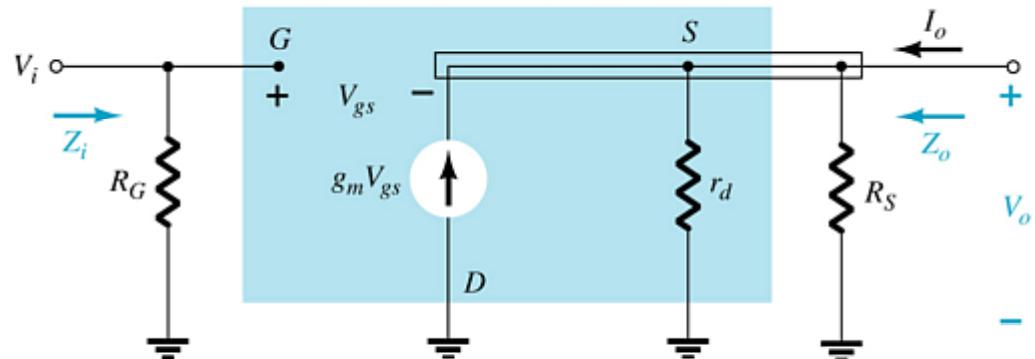

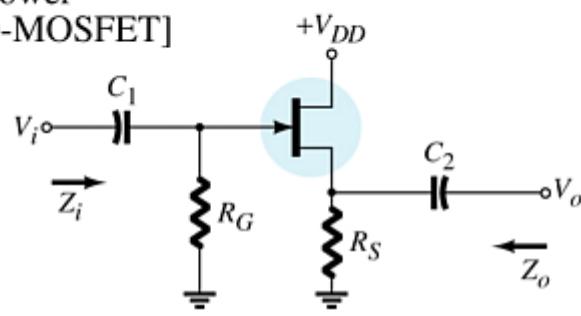

# Circuit suiveur de source (Drain-Commun)

Dans une configuration d'amplificateur à drain-commun, l'entrée est dans la grille, mais la sortie est dans la source.

Il n'y a pas de décalage de phase entre l'entrée et la sortie.

# Impédances

Impédance d'entrée:

$$Z_i = R_G$$

Impédance de sortie:

$$Z_o = r_d \parallel R_S \parallel \frac{1}{g_m}$$

$$Z_o \cong R_S \parallel \frac{1}{g_m} \quad | \quad r_d \geq 10R_S$$

Gain en tension:

$$A_v = \frac{V_o}{V_i} = \frac{g_m(r_d \parallel R_S)}{1 + g_m(r_d \parallel R_S)}$$

$$A_v = \frac{V_o}{V_i} = \frac{g_m R_S}{1 + g_m R_S} \quad | \quad r_d \geq 10$$

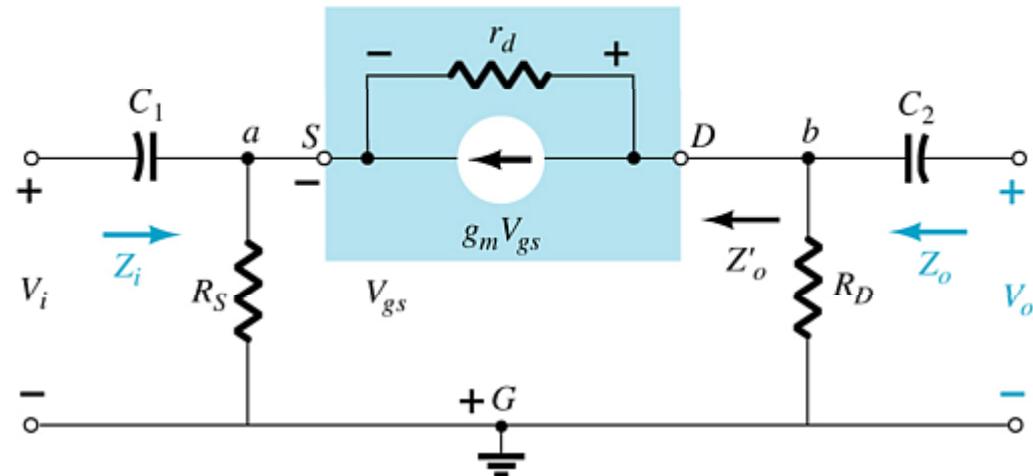

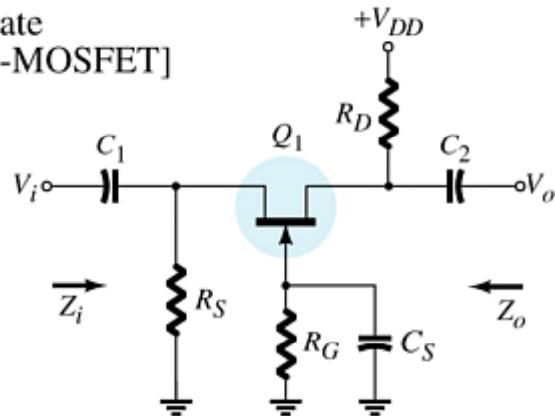

# Circuit à grille-commune

L'entrée est dans la source et la sortie est dans le drain.

Il n'y a pas de décalage de phase entre l'entrée et la sortie.

# Calculs

Impédance d'entrée:

$$Z_i = R_S \parallel \left[ \frac{r_d + R_D}{1 + g_m r_d} \right]$$

$$Z_i \cong R_S \parallel \frac{1}{g_m} \Big|_{r_d \geq 10R_D}$$

Impédance de sortie:

$$Z_o = R_D \parallel r_d$$

$$Z_o \cong R_D \Big|_{r_d \geq 10}$$

Gain en tension:

$$A_v = \frac{V_o}{V_i} = \frac{\left[ g_m R_D + \frac{R_D}{r_d} \right]}{\left[ 1 + \frac{R_D}{r_d} \right]} \quad A_v = g_m R_D \Big|_{r_d \geq 10R_D}$$

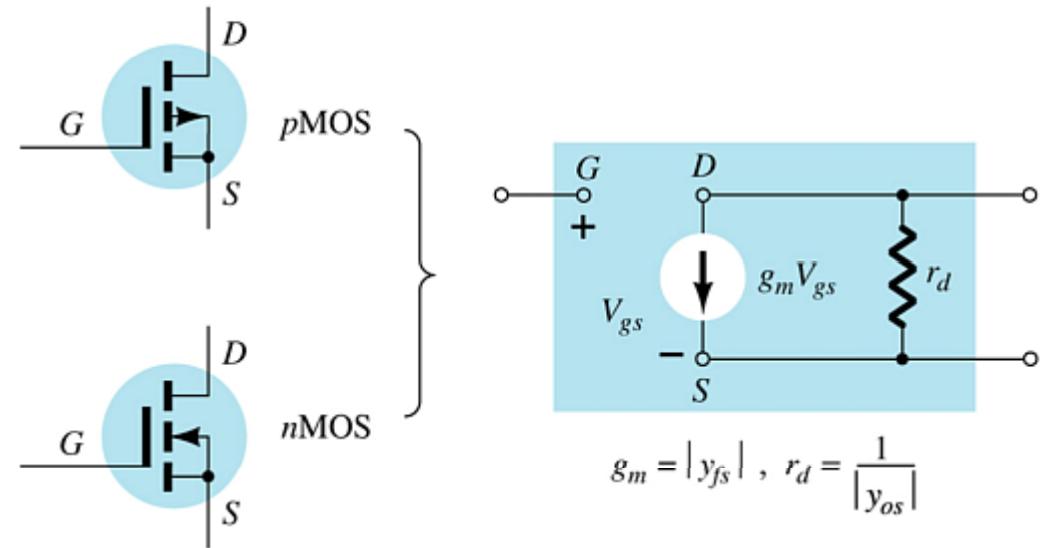

# Equivalent AC du type D-MOSFET

# Equivalent AC du Type E-MOSFET

**$g_m$  et  $r_d$  se trouvent dans la fiche des spécifications du FET.**

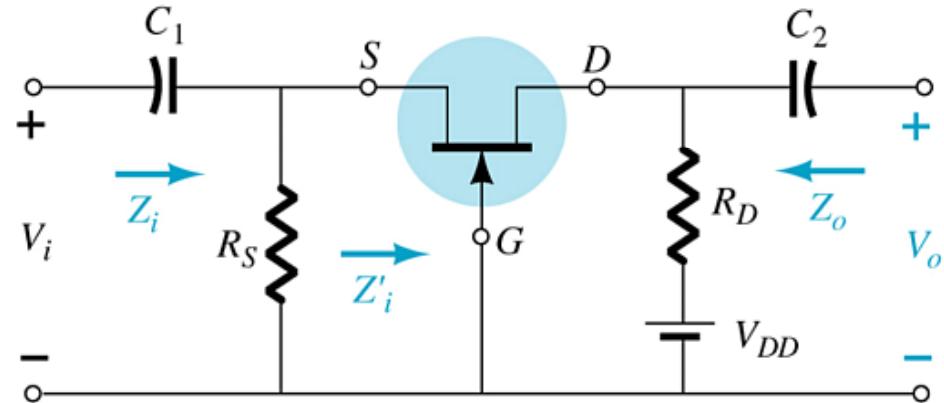

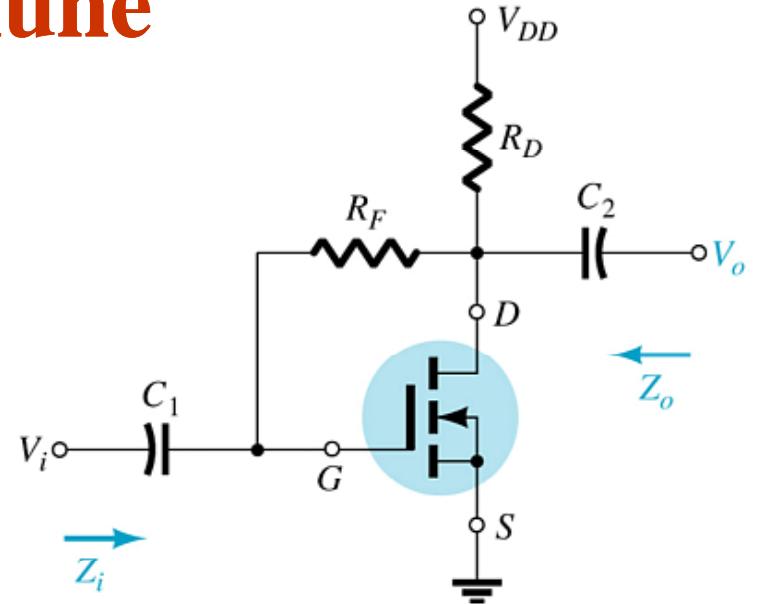

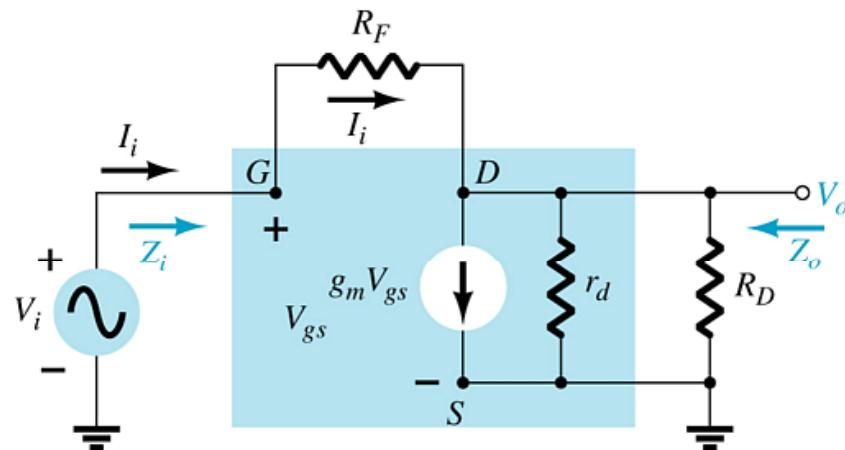

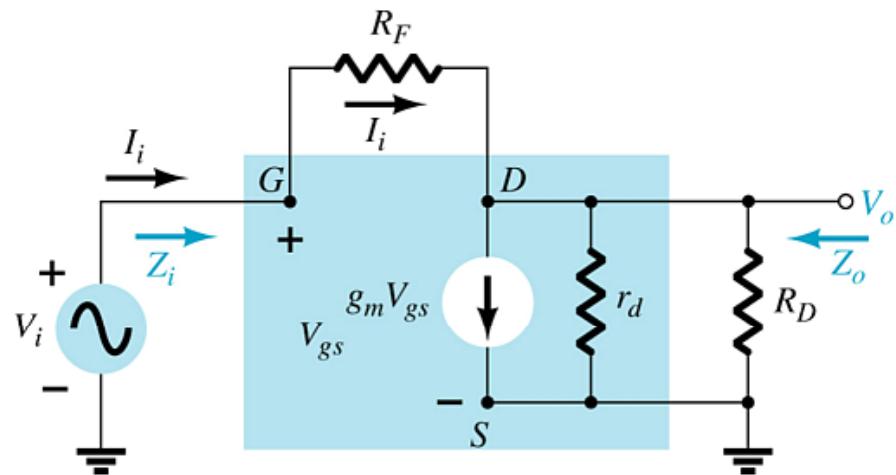

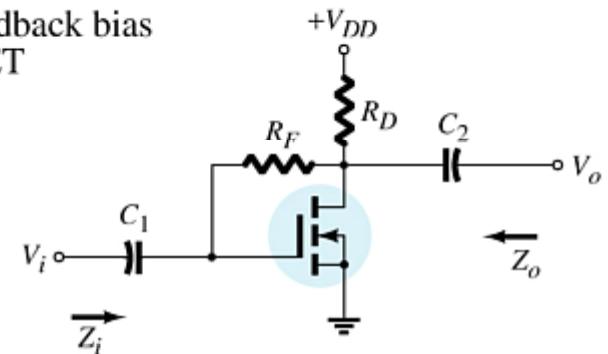

# Polarisation par rétroaction du drain Source-commune

Il y a un changement de phase de  $180^\circ$  entre l'entrée et la sortie.

# Calculs

**Impédance d'entrée:**

$$Z_i = \frac{R_F + r_d \parallel R_D}{1 + g_m(r_d \parallel R_D)}$$

$$Z_i \cong \frac{R_F}{1 + g_m R_D} \quad | \quad R_F \gg r_d \parallel R_D, r_d \geq 10R_D$$

**Impédance de sortie:**

$$Z_o = R_F \parallel r_d \parallel R_D$$

$$Z_o \cong R_D \quad | \quad R_F \gg r_d \parallel R_D, r_d \geq 10R_D$$

**Gain en tension:**

$$A_v = -g_m(R_F \parallel r_d \parallel R_D)$$

$$A_v \cong -g_m R_D \quad | \quad R_F \gg r_d \parallel R_D, r_d \geq 10R_D$$

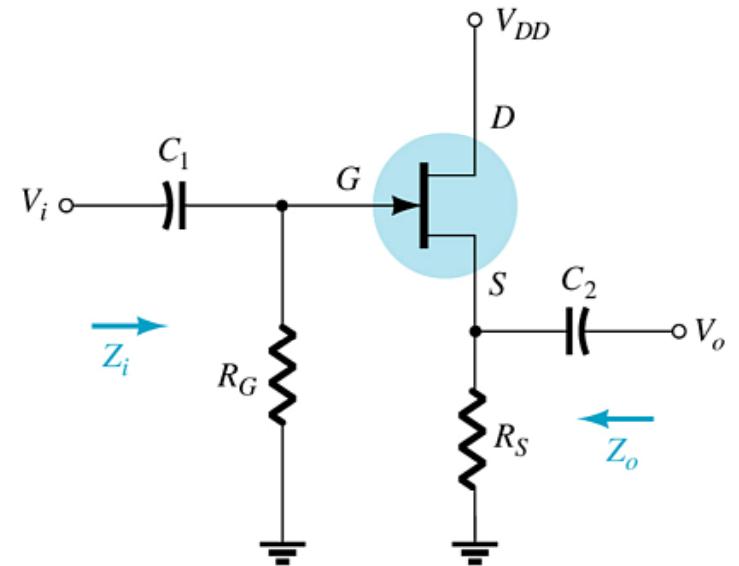

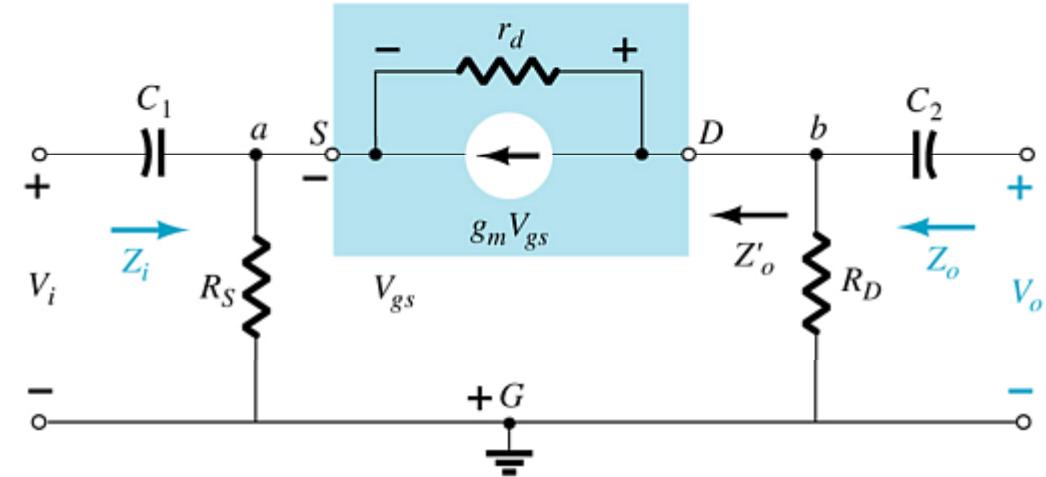

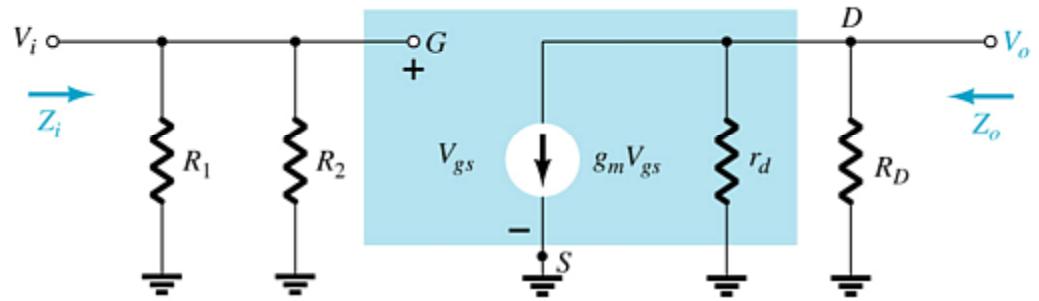

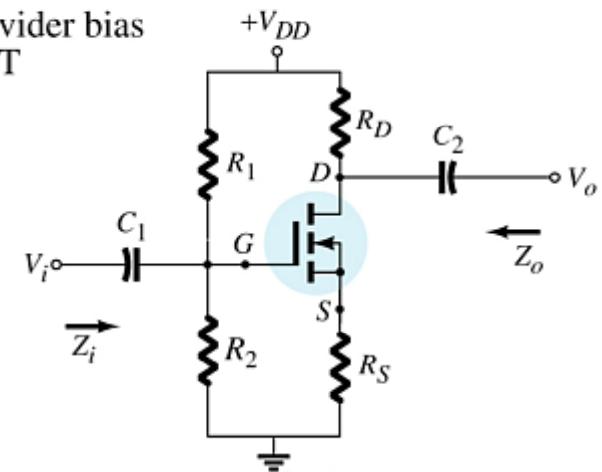

# Polarisation Diviseur de tension source-commune

# Calculs

Impédance d'entrée:

$$Z_i = R_1 \parallel R_2$$

Impédance de sortie:

$$Z_o = r_d \parallel R_D$$

$$Z_o \cong R_D \Big| r_d \geq 10$$

Gain en tension:

$$A_v = -g_m (r_d \parallel R_D)$$

$$A_v \cong -g_m R_D \Big| r_d \geq 10 R_D$$

# Table résumé

Source-follower

[JFET or D-MOSFET]

Drain-Feedback bias

E-MOSFET

Common-gate

[JFET or D-MOSFET]

Voltage-divider bias

E-MOSFET

[more...](#)

# Table résumé

Fixed-bias

[JFET or D-MOSFET]

Self-bias

Unbypassed  $R_S$

[JFET or D-MOSFET]

Self-bias

bypassed  $R_S$

[JFET or D-MOSFET]

Voltage-divider bias

[JFET or D-MOSFET]

# Dépanage

## Vérifier les tensions DC:

Si elle n'est pas correcte, vérifier les résistances, le FET. Aussi vérifier que le condensateur de couplage entre les étapes est OK.

## Vérifier les tensions AC:

Si elles ne sont pas bonnes vérifier le FET, les condensateurs et l'effet de la charge sur l'étape suivante

# Applications pratiques

Mélangeur Audio

Réseaux par décalage de phase

Système de détection de mouvement